七位半高精度DAQ如何设计?(YUNSWJ 重写版)

哈喽~今天做一个测试,重写:

这篇去年的文章

这篇去年的文章

不知道怎么的,今年就捅了万用表的窝,都是干 DMM 的:

对于一篇纯粹的文章,这个数据蛮不错

对于一篇纯粹的文章,这个数据蛮不错

虽然 ADI 写的已经很好了,但是我个人觉得差点“接地气”的意思(指还是不够细),那我就负责做补充任务。

新的时代,新的选择

能不能不用传统那套很复杂的多斜率积分 ADC 架构,而是用现代高性能 SAR ADC + 超低漂移基准 + 精密匹配网络 + 零漂移放大器,做出接近七位半、甚至逼近八位半表现的高精度采集链?

这篇文的答案是:可以,而且效果相当好。

看看积分ADC

K2000 的 U165

K2000 的 U165

高精度的 ADC 用积分 ADC 的优点就是 INL 和时间相关,一些五位半都是用的积分 ADC,只能说不卖我们消费者而已,这些大厂肯定是在互相流转。

先说文章到底在讲什么

文章开头先交代了背景:高精度 DAQ 用来采集电子设备和传感器的信号,服务于实时处理、硬件在环、自动测试、数据记录等。真正难的是,当目标精度提高到七位半甚至更高时,传统方案一般会走分立式多斜率积分 ADC路线,因为它在超高精度 DMM 里很常见;但这种方案设计、调试、热管理、基准处理都比较复杂。与此同时,24 位 Σ-Δ ADC 虽然已经大量用于六位半 DMM,但要再往上走,线性度和基准源就成了主要瓶颈。

所以 ADI 这里给出的思路,不是继续走“经典老派积分型”,而是换一条路:把几颗器件拼成一条高精度模拟前端链,去冲击 7.5 digit DAQ。

为什么是这几颗芯片?

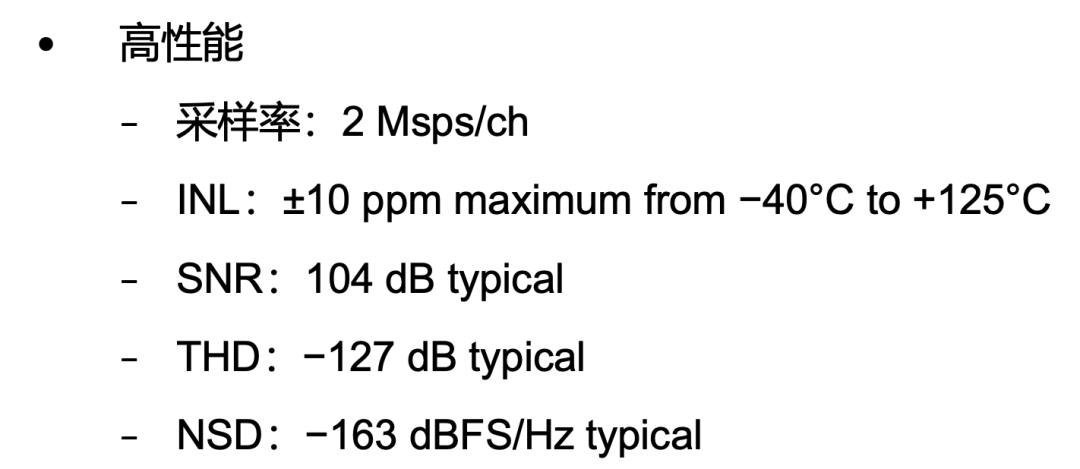

AD4630-24:高线性、高速 SAR ADC 是核心

文章把 ADC 放在第一位,因为这是整条链的“量化核心”。

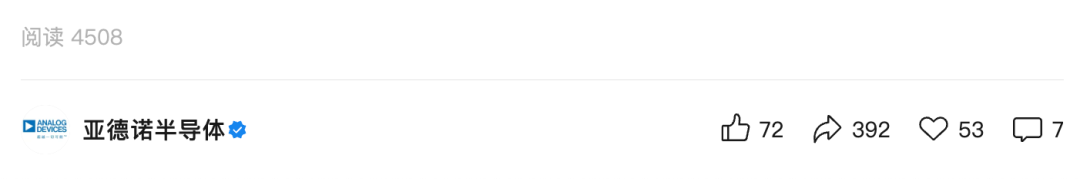

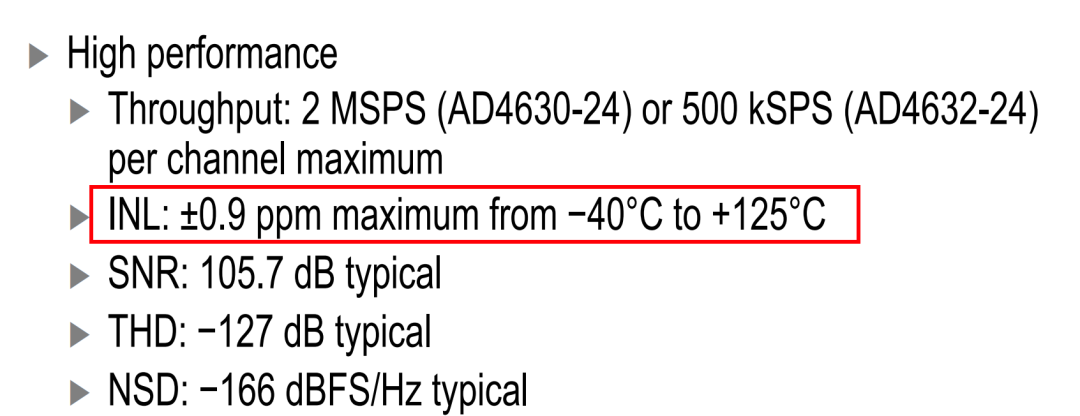

文中给出的信息是:24 位,2 MSPS,最大 ±0.9 ppm INL,Easy Drive 输入,宽共模输入范围,内置平均滤波器支持高达 30 位数据输出。

我个人觉得倒可能不一定是 0.9PPM

我个人觉得倒可能不一定是 0.9PPM

我觉得是想突显在 1PPM 之下这个意思。

还是太牛逼了

还是太牛逼了

这里最关键的不是“24 位”这几个字,而是:

真正关键的是 INL 很低

七位半系统,最怕的是“分辨率看起来高,但线性度不够”;如果 ADC 的 INL 很差,平均再久也只能把随机噪声压下去,压不掉系统性的非线性误差。(这里我留了一篇文章)

所以 ADI 选 AD4630-24,本质上是为了拿到:足够高的采样速率,很好的线性度,再配合平均/抽取后,把噪声继续压低;也就是说,这不是拿 2MSPS 去做高速波形采集,而是拿高速采样换静态精度。这点是整篇文章的设计哲学之一。

因为单纯的看 INL,还是有 ADC 做到了 1PPM 里面的:

型号 | 分辨率 | 架构 | 典型 INL | 最大 INL |

|---|---|---|---|---|

AD4630-24 | 24-bit | SAR | ±0.1 ppm | ±0.9 ppm |

LTC2500-32 | 32-bit | SAR | ±0.5 ppm | ±2 ppm |

LTC2378-20 | 20-bit | SAR | ±0.5 ppm | ±2 ppm |

AC9610 | 24-bit | SAR | -- | ±0.9 ppm |

我正好有海思的 ADC 手册

我正好有海思的 ADC 手册

那这个就稍微差点;所以这里的高采样还是要去平均一些噪声的。

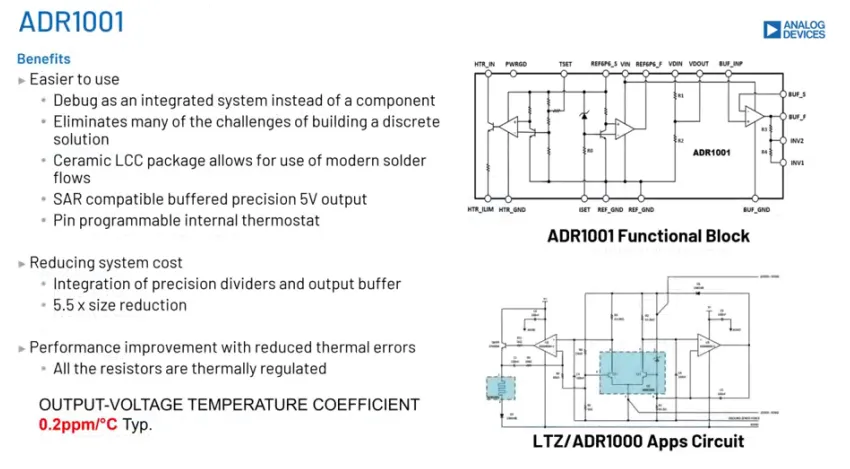

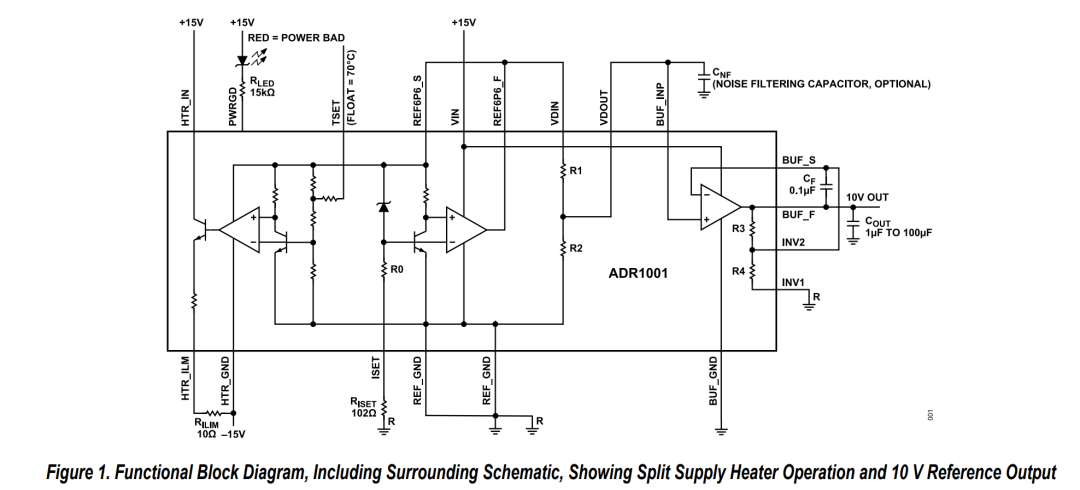

ADR1001

文章花了不少篇幅对比基准源,说明在七位半系统里,基准已经不是简单配一个 REF 芯片就结束了。

image.png

文中列了 ADR1399、ADR1000、ADR1001 等基准,并总结说:ADR1001 在输出噪声、温漂、长期漂移方面都处于顶尖水平,而且它是高集成方案,使用方便;温漂性能可以和 LTZ1000 媲美,集成了 buffer 和精密电阻,减少大量分立器件。

这个信息很重要,因为高精度系统里,基准不是孤立的一颗芯片,而是一个“小系统”:基准本体噪声,输出缓冲器的漂移和噪声,精密分压网络,热耦合,周边焊盘和铜皮的热梯度,长期稳定性。

传统 LTZ1000 类方案性能很强,但外围复杂,热设计要求高;ADR1001 的价值在于:把很多原本需要自己用分立元件做、而且很容易做砸的部分,直接集成进去了;这样系统误差源更少,也更容易复现。

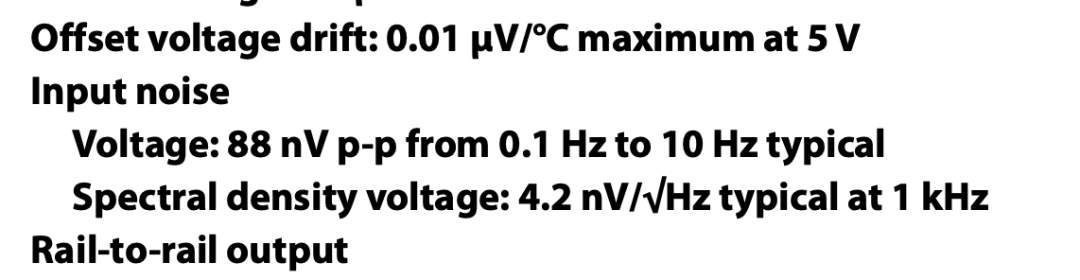

ADA4523-1:前端放大器不是只看零漂,还要看噪声

文章对比了 ADA4522 和 ADA4523-1。 ADA4523-1 的特点包括:4.2 nV/√Hz 电压噪声密度,88 nV p-p 低频噪声,10 nV/℃ 偏置电压漂移,5 MHz GBW,比 ADA4522 更宽。

为什么这里用零漂移放大器而不是普通低噪声运放?

因为七位半这种系统里,会同时碰到两类误差:直流误差 / 温漂 / 零点漂移+低频噪声 / 1/f 噪声

零漂移运放能把 DC 稳定性做得非常好,但很多零漂移器件会有斩波残留、宽带噪声或频谱毛刺的问题;这篇文章强调 ADA4523-1,是因为它把“零漂”和“低噪声”这两件事都做到了比较高水平,所以适合放在这类精密 DAQ 前端里。

既要又要才是 DMM 的常态

既要又要才是 DMM 的常态

LT5400

(老演员了,还是写写吧~)文章说 LT5400 具有:0.01% 电阻匹配度,0.2 ppm/℃ 匹配温漂,同时还有很好的长期稳定性,这在七位半系统里极其关键;因为前端要把 ±10V 输入 转换成 ADC 需要的 0~5V 输入,这通常不是简单放大,而是:做比例缩放,做共模平移,做差分构造,做精密增益设置,这些动作都依赖电阻比。

另外整体也不能太差:

几乎都是定制的电阻

几乎都是定制的电阻

在这类系统里,很多误差并不是来自“单个电阻值不准”,而是来自:比值不准,比值随温度变化,同一个网络不同电阻热漂不一致,长期老化不同步。

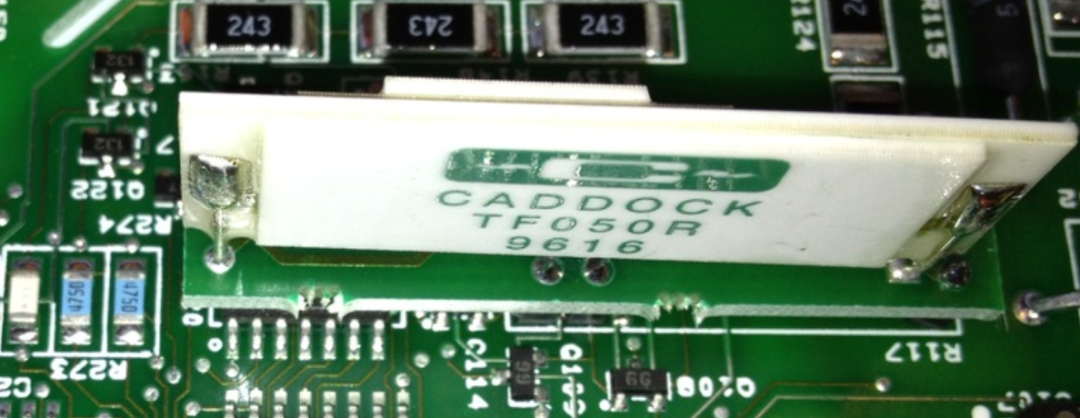

当然了,真实系统我见过这个 5400 的还真不多:

见的都是这样的

见的都是这样的

所以LT5400 的意义,就是把“电阻比”的问题做成一个热耦合良好的整体,在 DMM 里面比值稳定,比单个阻值绝对准确更重要。

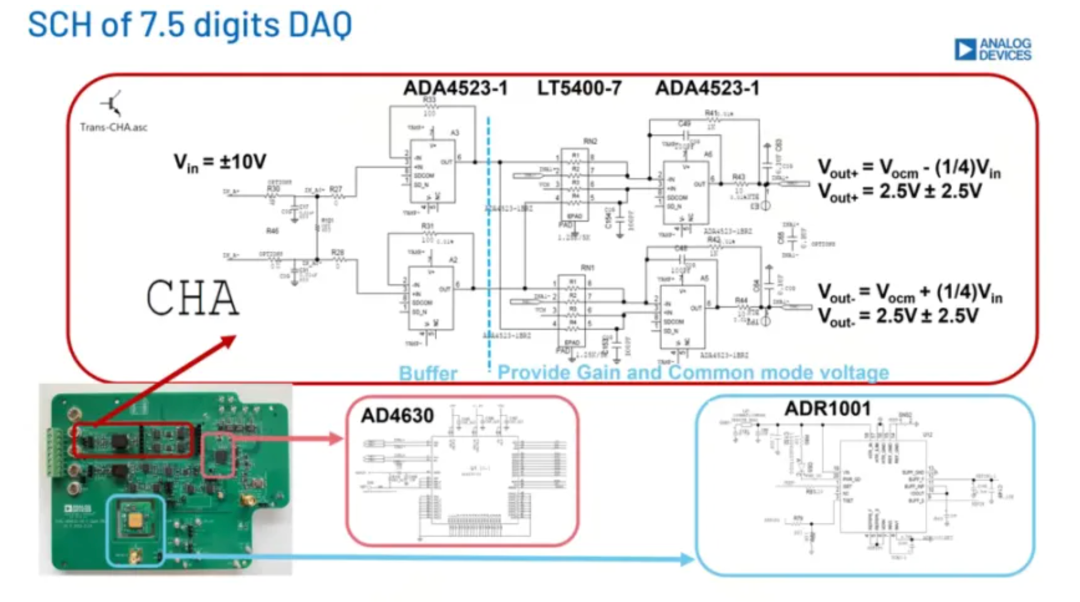

整条信号链是怎么工作的

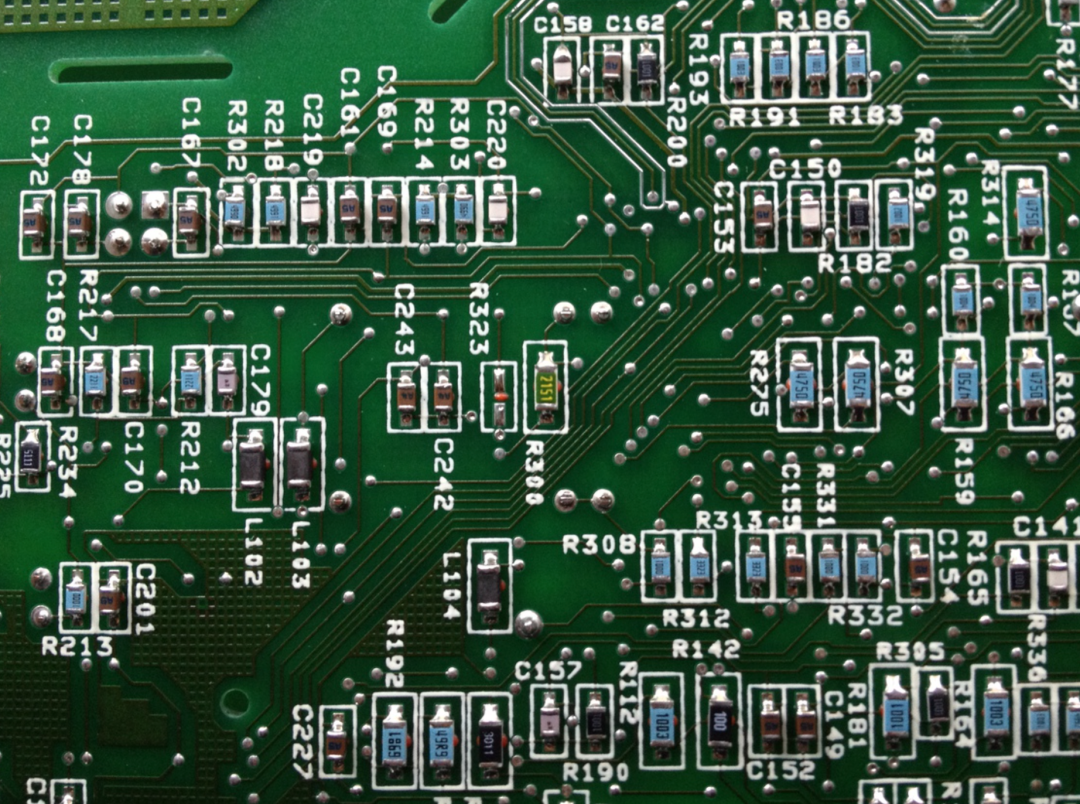

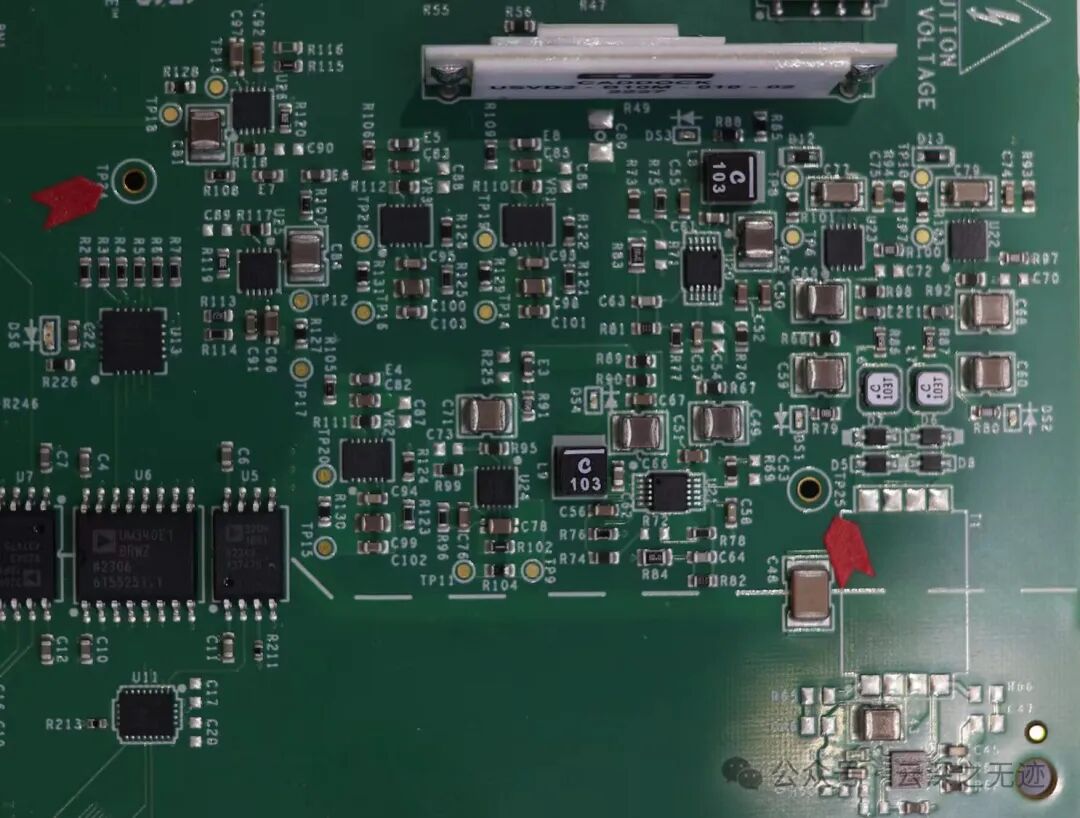

看不清也无所吊谓,很简单,主要是 Layout

看不清也无所吊谓,很简单,主要是 Layout

输入 ±10V → 信号调理(ADA4523 + LT5400)→ 变成 ADC 可接受的 0~5V → AD4630-24 采样 → ADR1001 提供高稳定基准。

从图里还能看出,它并不是纯粹把信号缩小,而是做了两件事:

增益/衰减处理

把 ±10V 量程压缩到 ADC 允许范围。

共模电平平移

图中明确写了输出关系大致是:

并给出 附近。也就是说,本来是双极性输入,最后被搬运成围绕 2.5V 的差分信号送入 ADC;好处是:能兼容 ADC 的输入共模要求,差分输入更利于抑制共模干扰,更容易做高精度比例变换。

这套设计为什么理论上能冲七位半?

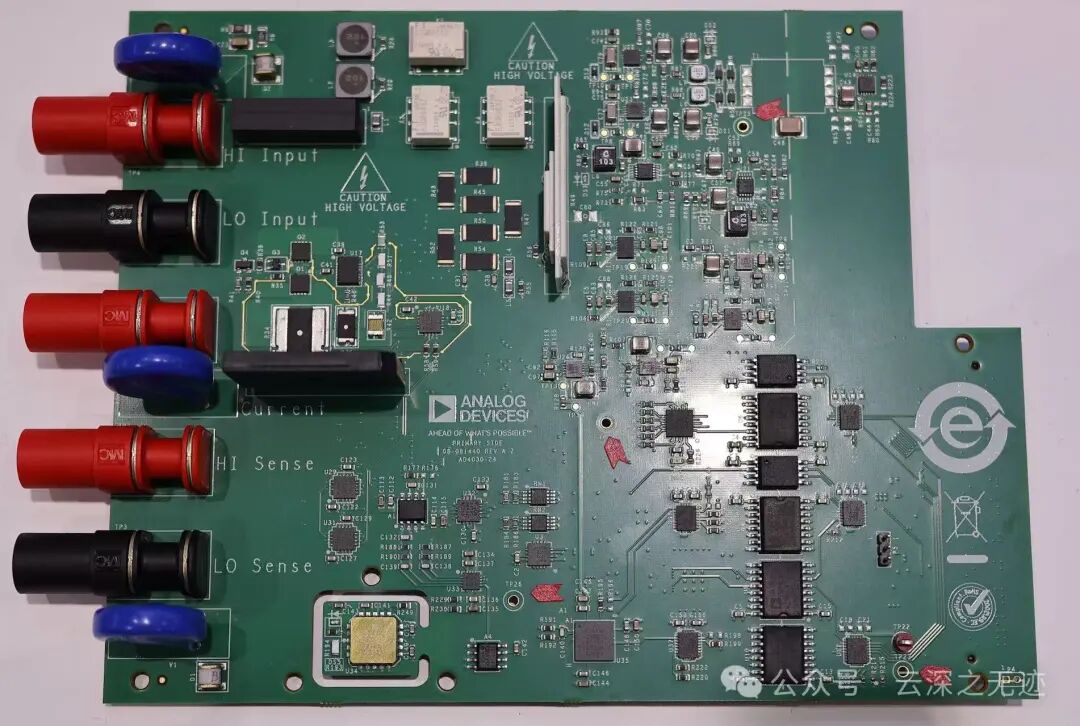

说话的艺术就在这里,其实这个选器件是一方面,另外一方面是看系统设计,真实的板子上面有大量的隔离以及各种 guard。

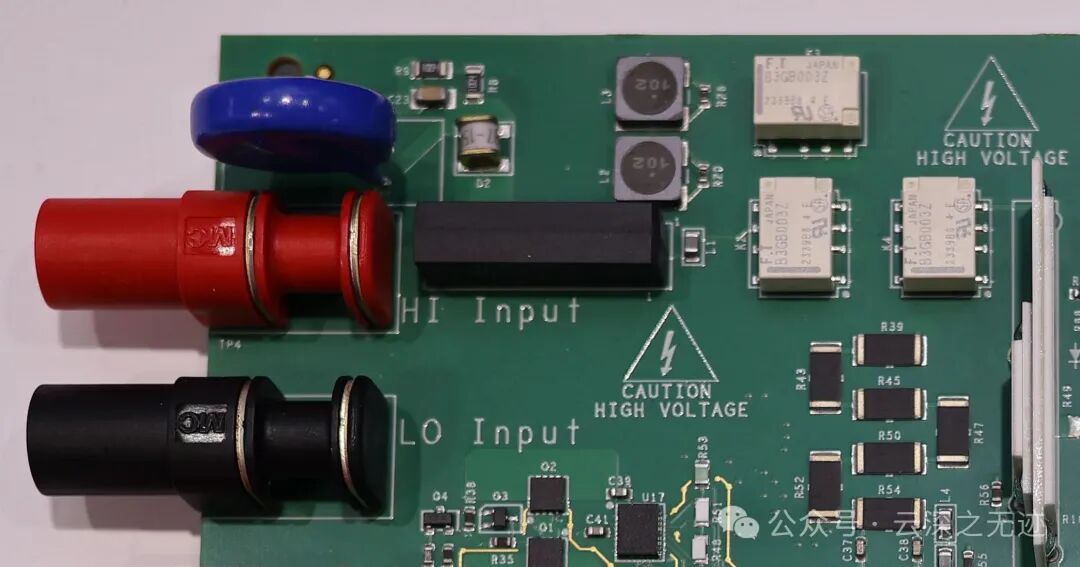

感谢我吧,我去现场拍回来了

感谢我吧,我去现场拍回来了

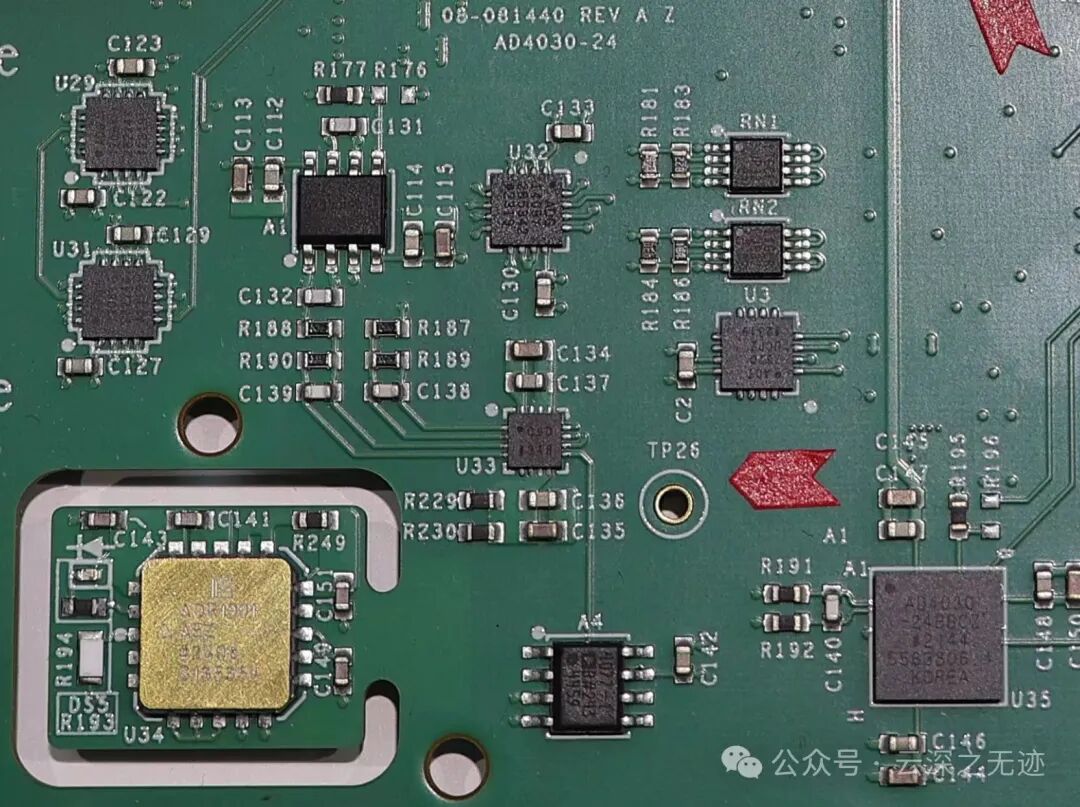

一眼 FPGA 口子,因为 ADC 不是省油的灯

一眼 FPGA 口子,因为 ADC 不是省油的灯

还得是差分

还得是差分

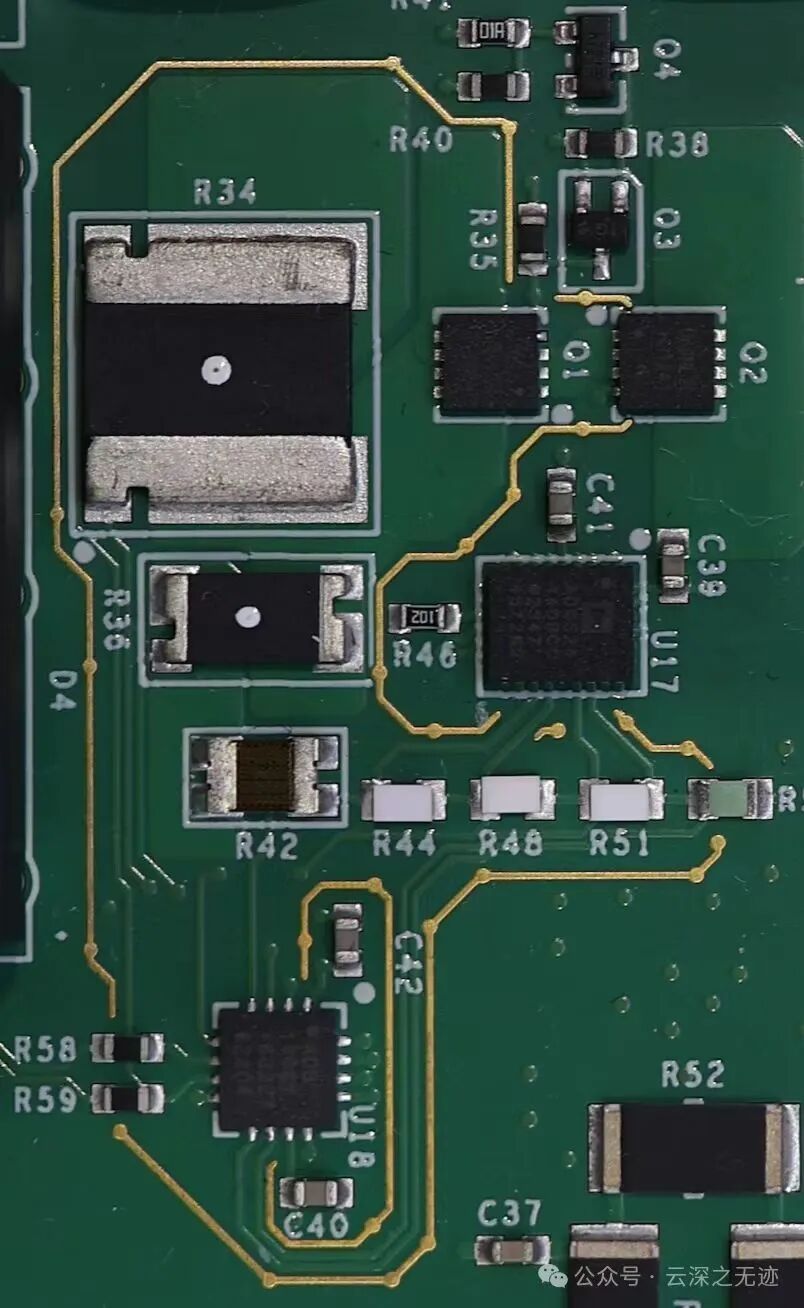

就这个走线,看着真的是美滋滋

就这个走线,看着真的是美滋滋

这是这颗基准,比较孤单

这是这颗基准,比较孤单

看见了吧,电阻也是定制的

看见了吧,电阻也是定制的

总之就是工程细节更加的重要;总之这篇文章背后的原理,其实可以概括成一句话:

高速、高线性的 SAR ADC + 超低漂移基准 + 低漂移低噪声前端 + 高匹配电阻网络 + 平均/PLC 输出策略 = 高位数直流测量能力

具体展开就是四点。

高速采样拿来换低噪声

AD4630-24 本身采样率高,系统不是直接原样输出,而是通过平均,最后用 10 PLC / 100 PLC 这样的慢输出速率来压低噪声;这和 DMM 的 NPLC 思路是相通的:内部采得很快,外部出得很慢。

ADC 线性好,所以平均后不会被 INL 限死

如果 ADC INL 差,平均只能得到更稳定的错误;这里 AD4630-24 的低 INL,使它适合作为七位半链路的量化核心。

基准和电阻比共同决定温漂和长期稳定性

单纯噪声低还不够,温漂和 24 小时漂移也要控制;这里 ADR1001 + LT5400 这一对,实际上是系统稳定度的基础。

前端放大器决定你能不能把理论性能真正搬到板子上

ADC 再强,如果前端带来 1/f 噪声、漂移、输入偏置误差、热电势,最后也会把有效位毁掉,ADA4523-1 的任务就是尽可能不拖后腿。

这篇文章呢,很多人看完会误以为:

“那我照着这套就能做出一台八位半万用表了。”其实不是。。。。

真正商品级 DMM 还要解决:输入保护,量程切换,电压/电流/电阻多功能,开关热电势,漏电路径,机械继电器/簧片继电器误差;绝缘、爬电、EMC,自校准和长期补偿。

测试结果怎么理解?

下面是整篇文章最有价值的部分。

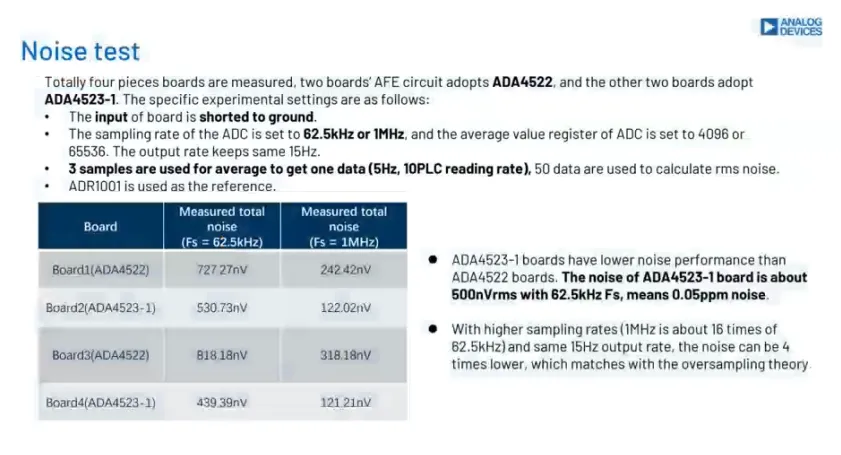

噪声测试

测试条件:输入短路

采样率:62.5 kHz 和 1 MHz

输出速率:10 PLC

image.png

在 62.5 kHz 采样率下,使用 ADA4523 的板子,噪声大约 500 nV RMS,相当于 0.05 ppm 噪声水平;采样率升到 1 MHz 后,在同样输出速率下,噪声大约降为原来的 1/4,这和过采样理论吻合。

这个结果很有意思。

为什么从 62.5k 到 1M,噪声变成 1/4?

因为采样率提高了 16 倍,对于随机噪声,平均后 RMS 大致按 下降,所以:

所以噪声降到原来的四分之一,非常合理。

500 nV RMS 是什么概念?

如果满量程参考成 10V 量级,那么:

这已经是很强的静态测量噪声水平了;换句话说,单从噪声角度看,这条链已经进入真正的七位半级别讨论范围。

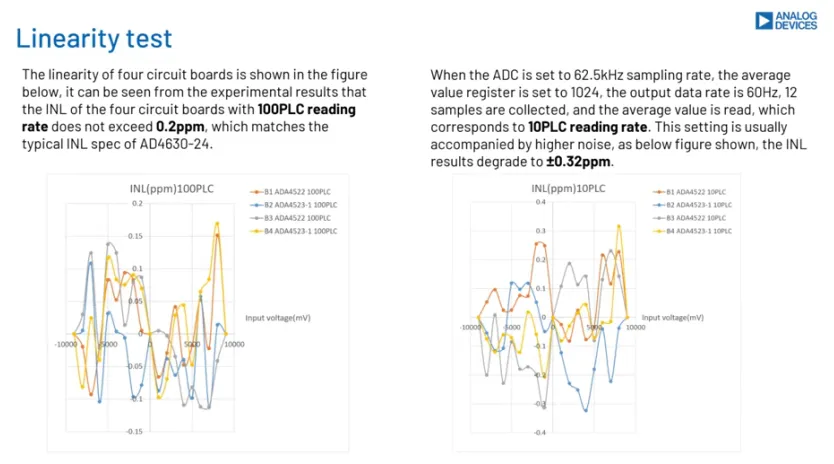

线性度测试

image.png

文章给出的结果是:

100 PLC 输出速率下,INL 不超过 0.2 ppm

10 PLC 输出速率下,INL 不超过 0.32 ppm

使用 ADR1399 时,INL 约 0.3 ppm

使用 AD4550D 时,INL 约 0.4 ppm。

这里要特别理解:

为什么 100 PLC 比 10 PLC 更好?

因为测试得到的线性度曲线会被噪声“抖动”污染;100 PLC 平均更久,随机噪声更低,所以看到的 INL 更接近真实 INL;10 PLC 速度更快,噪声更大,所以测出来的“INL”里掺了更多噪声分量,也就是说:这不一定意味着 ADC 本体线性变差了,更像是测量分辨率不够导致的表观线性恶化。

这也是高精度系统里常见的问题:测出来的误差,不一定全是被测系统的误差,也可能是测试噪声本身。(但是我更相信是不愿意说 ADC 的坏话,毕竟还要卖货)

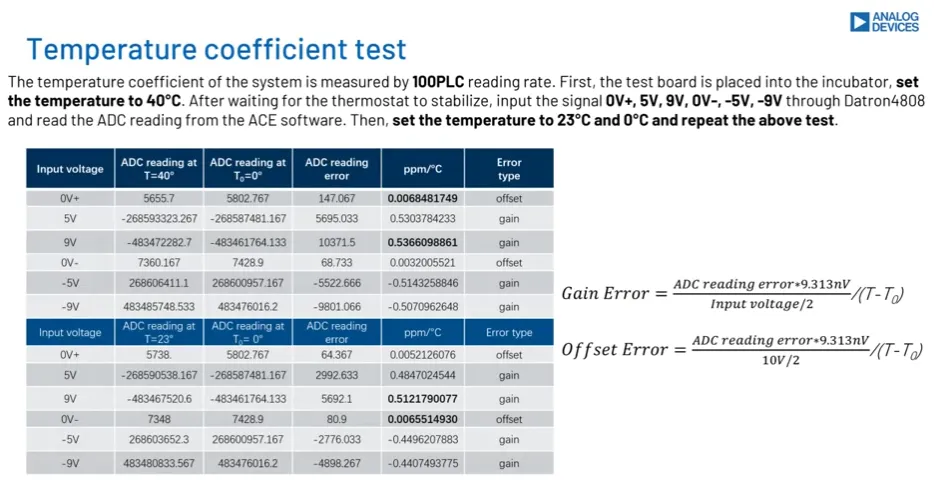

温度系数测试

image.png

测试条件:100 PLC 输出速率,温度设为 40℃、23℃、0℃设定不同输入电压,比较不同温度下读数变化;LT5400 决定了偏移误差,所以不同基准下偏移误差比较接近;LT5400 和基准都对增益误差影响较大,采用 ADR1001 时,增益误差特性更好,这一段非常值得细品。

为什么偏移主要由 LT5400 决定?

因为前端做了比例和共模搬移,任何电阻比不匹配、网络内部热梯度、输入级失配,都会投影到零点误差上;在这种结构下,偏移并不只是运放 Vos 的问题,而是整个差分比例网络的综合结果。

为什么增益受 LT5400 和基准共同影响?

增益本质是:

读数输入经过电阻比变换后的电压参考电压

所以电阻比漂 → 增益漂,参考漂 → 增益漂,这也是回答了高精度链路里,匹配网络和基准是同等重要的两个维度。

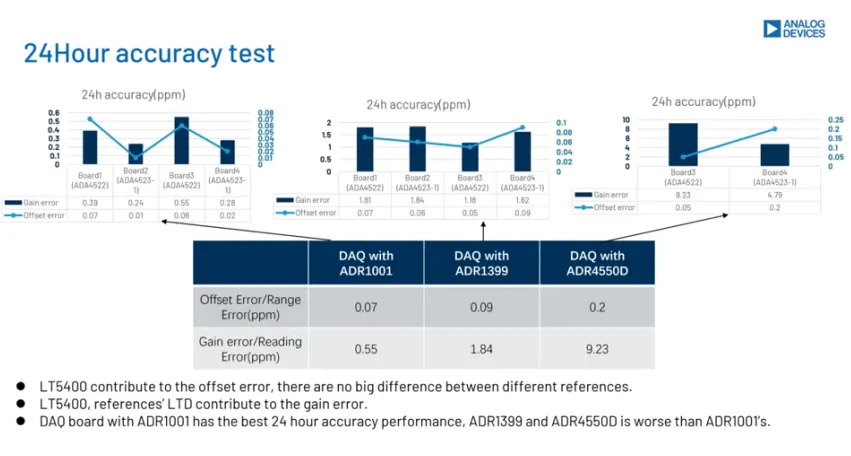

24 小时稳定性测试

image.png

文章说得很简洁24 小时稳定性测试里,ADR1001 基准的板子结果更好。

从图表上还能看出,ADR1001 对应的:offset error/range error 更小,gain error/reading error 更小;这说明 ADR1001 的优势不仅体现在“瞬时噪声”,更体现在:热稳定,长时漂移,整体系统误差收敛性;对于 DAQ/DMM 这种长时间记录或校准周期较长的系统,这一点比瞬时低噪声还重要。

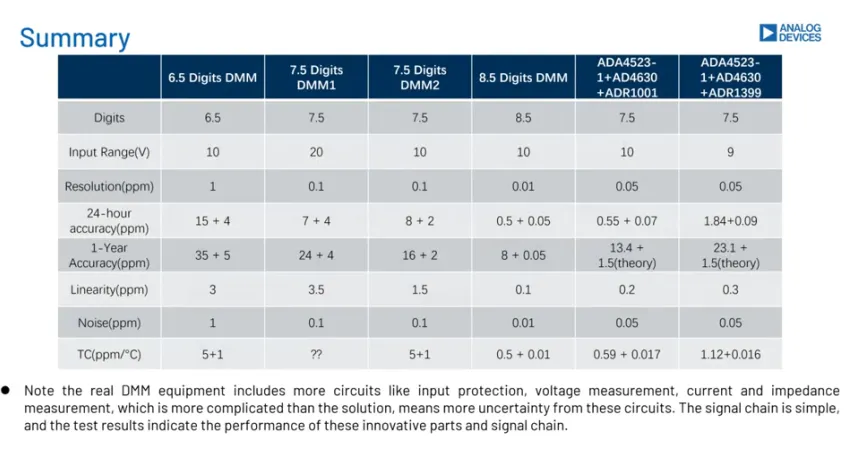

最后和市场 DMM 的对比

image.png

这次测试的 DAQ 结果介于七位半和八位半之间,但要注意,这只是信号链性能验证,真正商品级 DMM 还有很多附加电路和误差源。

这篇文章证明:

核心测量链路本身已经足够强,剩下的困难转移到了系统工程。

总结

七位半系统不再必须依赖传统多斜率积分 ADC,现代高线性 SAR ADC 已经开始具备竞争力。

高采样率在这里不是为了高速波形,而是为了过采样降噪,2 MSPS 是拿来换低噪声和高分辨率输出的。

线性度是冲七位半的硬门槛,光有 24 位分辨率完全不够,INL 要足够低。

基准已经是一个“系统模块”,不是一颗普通参考芯片;ADR1001 的价值在于高集成、低漂移、低噪声、易实现。

精密电阻网络对温漂、增益、零点都极其关键;LT5400 这种匹配网络在高精度设计里权重非常大。

前端运放要同时兼顾零漂和低噪声;ADA4523-1 是这篇文章里非常关键的一环。

100 PLC / 10 PLC 这种输出策略,本质是把 DAQ 做出 DMM 味道;慢速高精度读数,靠的是内部高速采样与平均。

可以把整篇文章理解为下面这个误差预算框架:

总误差静态线性参考噪声漂移增益基准前端运放噪声漂移低频与零点电阻比误差温漂增益与偏移电源热梯度布局系统实现平均残余噪声输出读数散布

而这篇文章做的事情,就是选一组器件,让上面每一项都压得足够低:

ADC:AD4630-24 压线性项

基准:ADR1001 压参考项

放大器:ADA4523-1 压漂移和低频噪声

电阻网络:LT5400 压比值误差

高采样 + PLC:压随机噪声

(有厂家愿意赞助点设备仪器器件什么的都可以,hhhh,本条信息常年有效)

之后我写建模的部分,待续。。。(假如阅读量好)

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-04-15,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录