如何在testbench结果中获得更多信息?

如何在testbench结果中获得更多信息?

提问于 2022-08-20 15:05:42

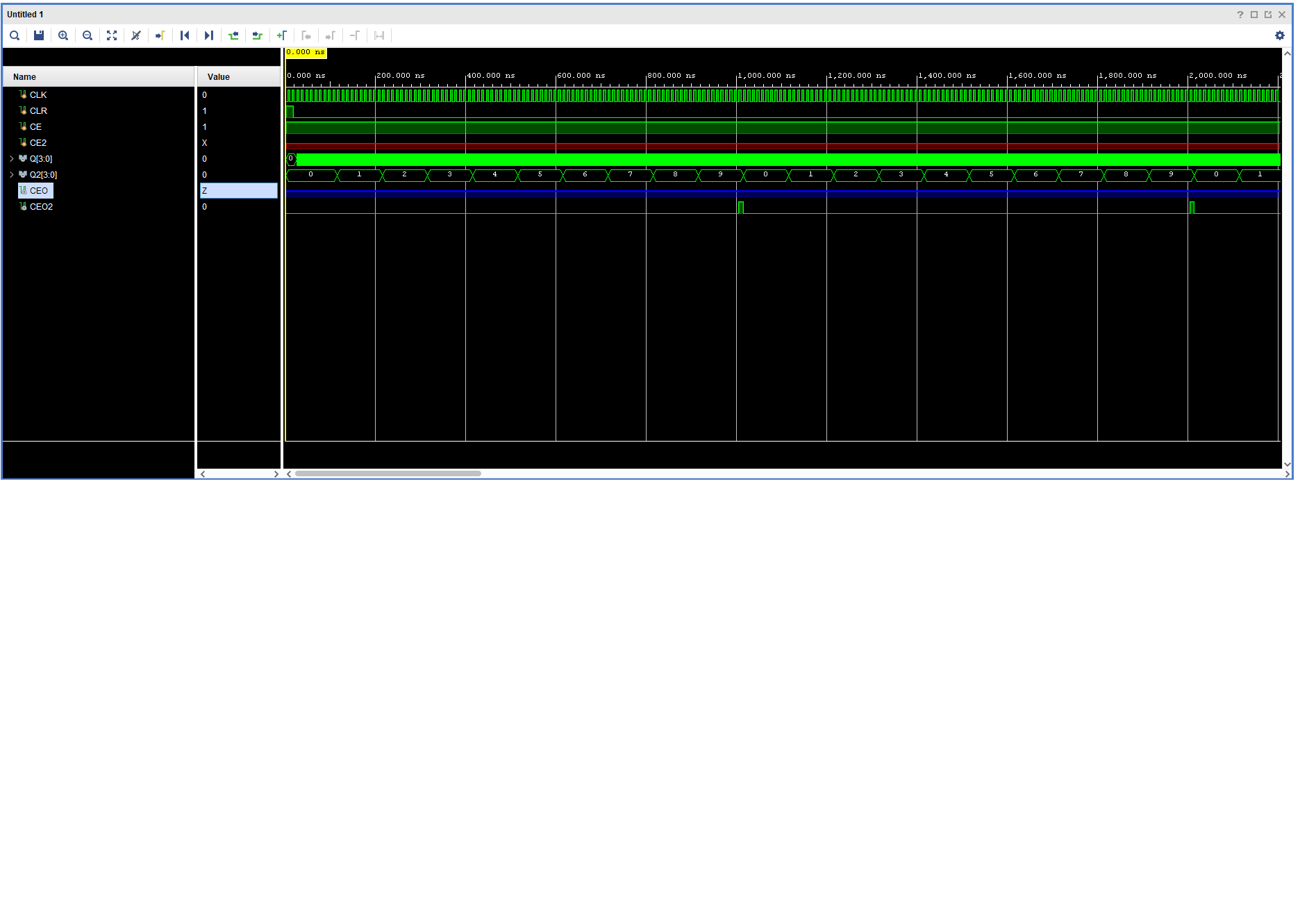

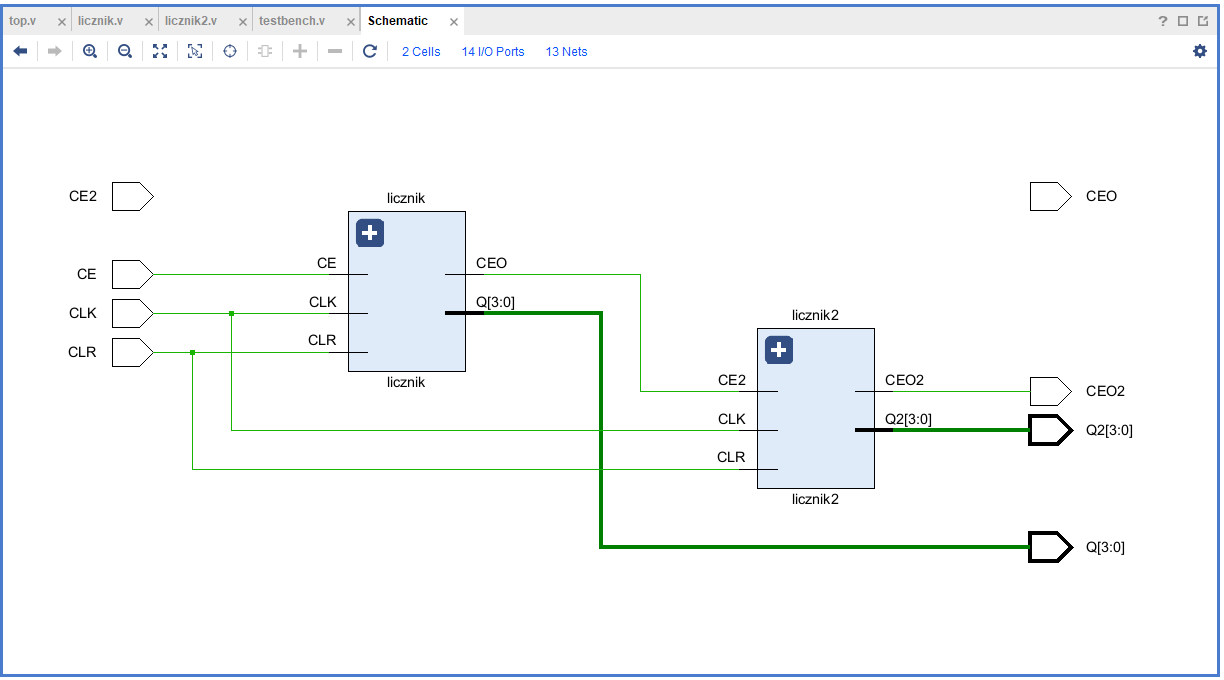

我意识到,这可能很容易解决,但我无法找到一个办法,使它的工作。我的问题是,在这种情况下,我如何获得CE2和首席执行官的视觉信号?我知道通过查看RTL计划,CE2和首席执行官并没有连接到引脚。我就是不能把他们联系起来。当第一个计数器到达9时,CE2应该打开,但在波形上,它总是X。当Q为9时,首席执行官应该打开,而在波形上,总是Z。这个电路只是为了自学。

Testbench

电路方案

顶部模块:

`timescale 1ns / 1ps

module top(

input CLK,

input CLR,

input CE,

input CE2,

output reg [3:0] Q,

output reg [3:0] Q2,

output wire CEO,

output CEO2

);

wire CLK;

wire CLR;

wire CENABLE;

wire CE2;

wire Q;

wire Q2;

wire CEO;

wire CEO2;

licznik licznik(.CLK(CLK),.CLR(CLR),.CE(CE),.CEO(CENABLE),.Q(Q));

licznik2 licznik2(.CLK(CLK),.CLR(CLR),.CE2(CENABLE),.Q2(Q2),.CEO2(CEO2));

endmoduleTESTBENCH:

`timescale 1ns / 1ps

module testbench;

reg CLK;

reg CLR;

reg CE;

reg CE2;

wire [3:0] Q;

wire [3:0] Q2;

wire CEO;

wire CEO2;

top UUT (

.CLK(CLK),

.CLR(CLR),

.CE(CE),

.CE2(CE2),

.Q(Q),

.Q2(Q2),

.CEO(CEO),

.CEO2(CEO2)

);

initial CLK=1'b0;

always #5 CLK=~CLK;

initial

begin

CLR = 1'b1;

CE= 1'b1;

#18 CLR = 1'b0;

end

endmodule第一个模块:

`timescale 1ns / 1ps

module licznik(

input CLK,

input CLR,

input CE,

output reg [3:0] Q,

output CEO

);

always @(posedge CLK or posedge CLR)

if(CLR)

Q <= 4'd0;

else begin

if(CE) begin

if(Q != 4'd9)

Q <= Q + 1;

else

Q <= 4'd0;

end

end

assign CEO = CE & (Q == 4'd9);

endmodule第二个模块:

`timescale 1ns / 1ps

module licznik2(

input CLK,

input CLR,

input CE2,

output reg [3:0] Q2,

output CEO2

);

always @(posedge CLK or posedge CLR)

if(CLR)

Q2 <= 4'd0;

else begin

if(CE2) begin

if(Q2 != 4'd9)

Q2 <= Q2 + 1;

else

Q2 <= 4'd0;

end

end

assign CEO2 = CE2 & (Q2 == 4'd9);

endmodule回答 1

Stack Overflow用户

回答已采纳

发布于 2022-08-20 15:44:35

我在两个模拟器上运行了您的代码,在这两个模拟器上都有编译错误。在EDAPlayground上尝试您的代码。

为了修复编译错误,我删除了模块top中的top声明。为了在CEO上解决Z的问题,我用CEO替换了CENABLE。下面是新的top模块:

module top(

input CLK,

input CLR,

input CE,

input CE2,

output reg [3:0] Q,

output reg [3:0] Q2,

output wire CEO,

output CEO2

);

licznik licznik(.CLK(CLK),.CLR(CLR),.CE(CE),.CEO(CEO),.Q(Q));

licznik2 licznik2(.CLK(CLK),.CLR(CLR),.CE2(CEO),.Q2(Q2),.CEO2(CEO2));

endmoduleCE2是X,因为它是一个非驱动输入。我想你可以把它删掉。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/73427760

复制相关文章

相似问题